Power distribution network (PDN) planning

首先我們要先了解電源平面及地平面,就像是共振腔體,不同的大小或形狀,都會有它的諧振模態,在電源分佈網路(PDN)的設計,其實簡單來說就是去設計電源端到抽載電容,這之間的的電源路徑上,是否在有效頻寬內達到目標阻抗(Target Impedance)的要求,如果超出目標阻抗的頻率點,遇到電源抽載所造成的SSN又剛好在那個頻率點,就會造成EMI問題如之前文章提到的PI Basic–Simultaneous Switching Noise (SSN)

電源分佈網路(PDN)是什麼?

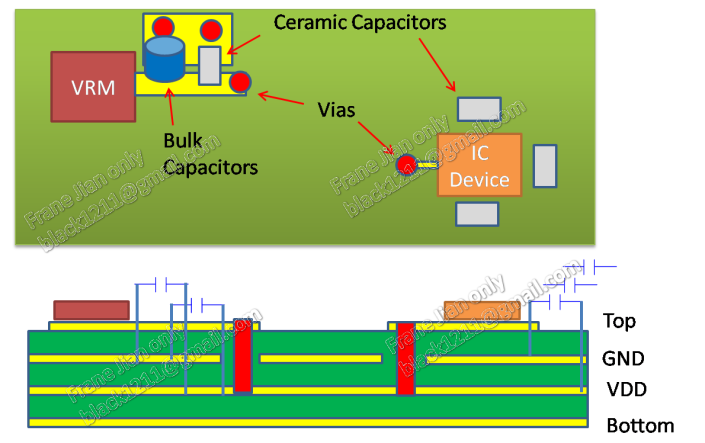

在電源系統,一定會有幾個重要部分,如下圖所示。

1.電壓調節模組(VRM)

2.電源路徑(線或平面)

3.抽載IC

4.旁路電容或解耦電容

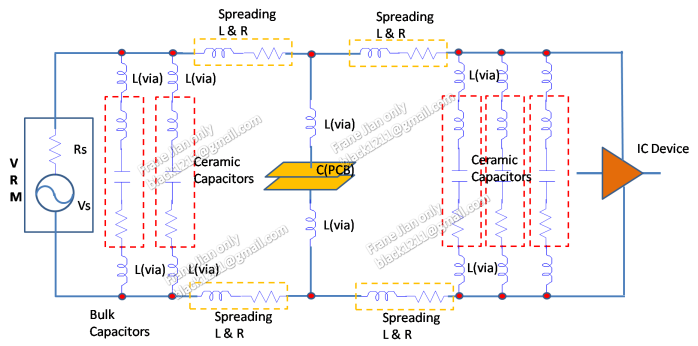

電源分佈網路(PDN)就是電源系統的整體路徑網路,為了簡易的分析PDN,可以將它簡化為下圖的等效電路,一般電壓調節模組(VRM)首先會先接固態電容(Bulk capacitors),再接解耦電容,接下來過孔到電源層傳送電源,在接近終端器件再過孔到表面層送電到器件IC。

處理PDN有幾種狀況在抽載的解耦電容擺法,其中有一些優劣,如下說明。

1.最好的解耦電容擺法為接近抽載IC,並限制電流路徑到抽載接腳,如之前文章提到的PI Basic–Power Layout Rule on Decoupling Capacitors,就如網站星空_電子站的PI Optimization, Part I章節提到的9.Add HF capacitor (2.2nF+3.9nF)的內容,高頻解耦電容放置接近抽載IC,並限制電流路徑,其效果最好。

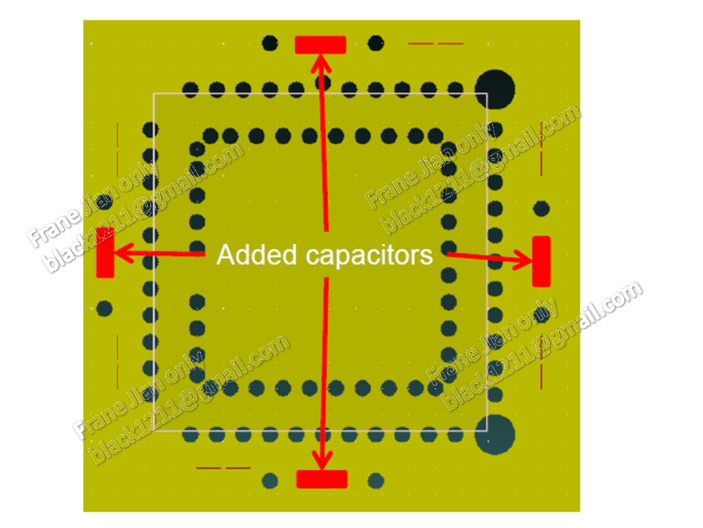

2.有時後解耦電容在一些高密度封裝的抽載IC,無法在接近接近抽載IC,並限制電流路徑,這時後就要靠諧振模態(Resonant Mode)分析最佳解耦電容擺放位置,但請注意利用諧振模態(Resonant Mode)分析最佳解耦電容擺放位置,主要是破壞低頻的諧振在PCB的共振腔模態,有可能低頻解了,反而高頻響應變差,文章後面會舉一個案例。

Ref.[1] Ansys Power Plane and Decoupling Optimization by Isaac Waldron

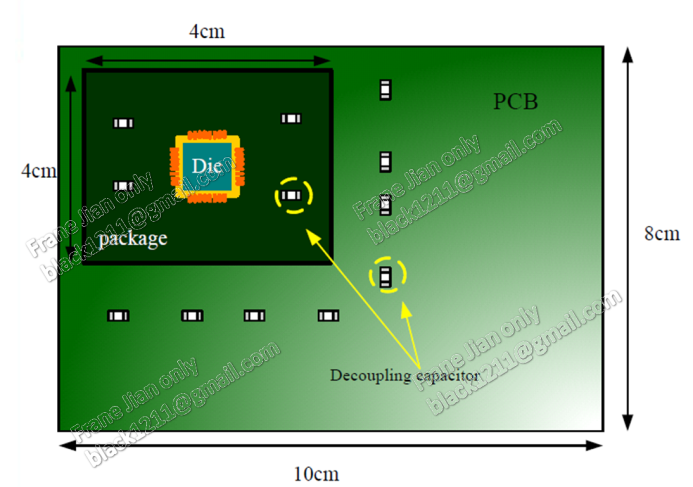

3.如果是做IC模組如CPU或DDR的封裝小板,這時後就無法將解耦電容去限制電流路徑到抽載接腳,這時後一般都會平均將解耦電容均勻放置在整個封裝小板上,這時後解耦電容的值及數量就變得很重要,目前所有能解PI的模擬軟體,都可以利用模擬軟體的工具去優化電容值及解耦電容數量。

Ref.[2] NTU Power Integrity and EMC Design for High-speed Circuits Packages by Tzong-Lin Wu, Ph. D.

目標阻抗Target Impedance

什麼是目標阻抗,簡單來說明,當你希望你的抽載電壓的漣波希望抑制到什麼區間,或是希望可以承載的高峰電流多少,就可以去定義目標阻抗該設定多少,如下面公式所示,採用Z參數。

Ztarget = (Power Supply Voltage * Allowed Ripple)/ Peak Current.

當然目標阻抗不可能固定一個值到全頻寬,一般來說會有階梯狀的目標阻抗值,其低頻的目標阻抗會比較低,越高頻目標阻抗會越高,如果設計方針(Design Guide)沒有特別規定,一般計算出來的目標阻抗只需要符合到1GHz即可。

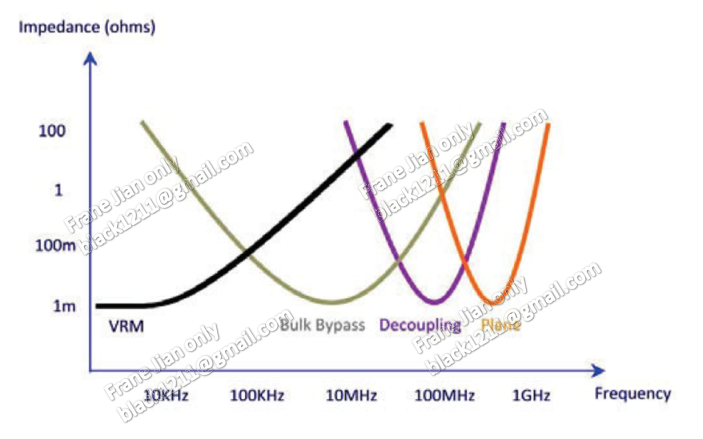

Note : 為什麼符合到1GHz即可,因為解耦電容及一般PCB設計,能解的問題最高大約在1GHz。如下圖所示。

所以大容值的固態電容,可以壓低較低的頻率的Z阻抗,較小的容值的陶瓷電容可以抑制較高的頻率的Z阻抗,如下圖所示。

Ref.[3] Power Distribution Network Planning by Barry Olney

使用Z組抗去分析抽載位置的電源通道狀況,在Z組抗在頻譜的表現值很低的情況,代表從抽載位置得到的電源通道是乾淨的,這樣抽載的IC即可得到較低的電源漣波(Power Ripple)。

範例 (ref. Ansys Siwave example)

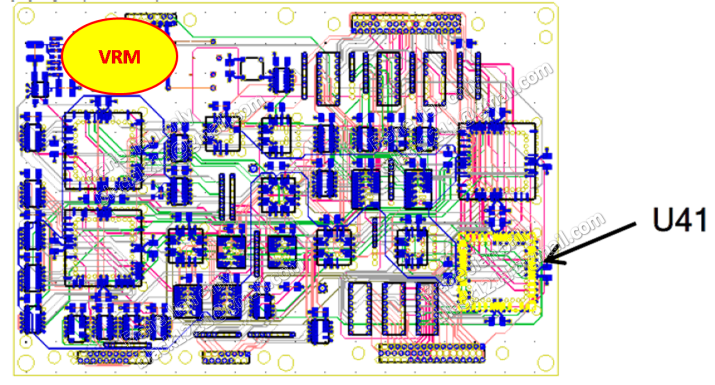

此範例為Ansys Siwave內附的範例檔,VRM電路在整個電路的左上方,另外抽載IC(U41)在整個PCB的右下方,如下圖所示。

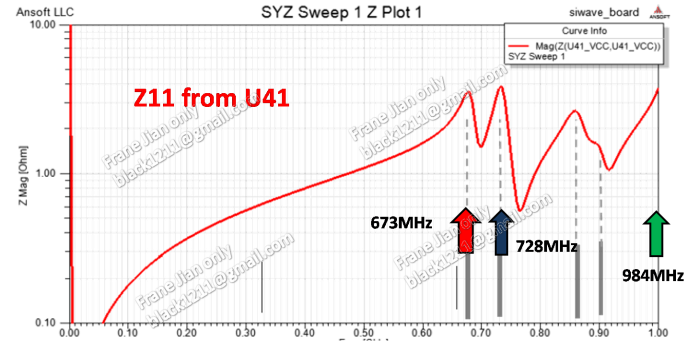

將抽載IC(U41)的電源接腳設定群組Port,並分析抽載IC(U41)電源群組Port的Z組抗,模擬完的結果如下圖,可以看到673MHz/728MHz/984MHz這三個頻率點的Z組抗特別高。

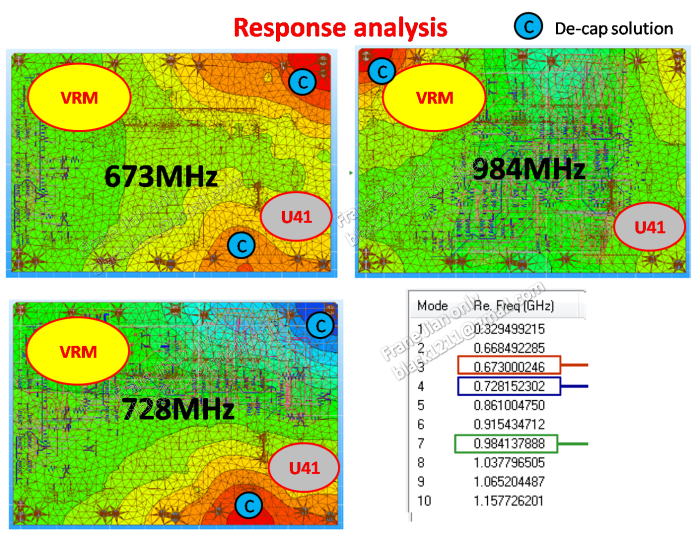

那該如何放置解耦電容去抑制這幾個頻率呢?可以利用Ansys Siwave的諧振模態(Resonant Mode)分析,去看PCB裡會產生這幾個頻率的位置,如下圖所示,將解耦電容放置在(C)的位置,並挑選SRF在這頻率點的電容,放置在這些位置上,去改變PCB的共振模態。

NOTE:請注意解完這幾個共振模態,因為這方法是去破壞PCB的共振模態,有可能會導致更高的頻率點又產生新的共振模態,所以要多方驗證。

Conclusion

1.抽載IC的解耦電容,最好放置靠近抽載IC,並限制電流路徑到抽載接腳,可以有最好的PDN設計,並抑制達較高的頻率。(很重要)

2.目標阻抗Target Impedance可以利用簡單的公式去定義出來,一般控制在1GHz以下即可。

3.使用諧振模態(Resonant Mode)分析去擺放解耦電容,是去破壞PCB的諧振模態,有可能會導致高頻的頻率產生新的諧振模態。

4.PDN設計是為了解決電源通道的品質,作好這段可以抑制電源漣波(Power Ripple),並抑制電源漣波所產生EMI的問題。

題外話:

1.結論提到的目標阻抗Target Impedance,一般考慮到1GHz以下即可,因為系統廠能解決的問題,一般也只能解到1GHz以下,原因是PCB調整的參數SRF也最高到接近1GHz而已,那要怎麼解超過1GHz高頻問題,除了動IC的設計外,一定要做好抽載IC的解耦電容,最好放置靠近抽載IC,並限制電流路徑到抽載接腳,這樣可以抑制較高頻的目標阻抗。

2.之前系統廠常常會遇到RFI/in-band noise,常常就是PI沒有做好,導致高頻的Z組抗過高,又遇到SSN的高頻雜訊剛好長在無線收發機的工作頻率,如果能做好抽載IC的解耦電容,最好放置靠近抽載IC,並限制電流路徑到抽載接腳,很有機會就解決這個問題。

參考文獻

Ref.[1] Ansys Power Plane and Decoupling Optimization by Isaac Waldron

Ref.[2] NTU Power Integrity and EMC Design for High-speed Circuits Packages by Tzong-Lin Wu, Ph. D.

Ref.[3] Power Distribution Network Planning by Barry Olney