Channel designer Co-design Equalizer

今天來談論的是關於信號完整性(SI)工程師或通道(Channel)工程師如何協同設計Equalizer。

現今的SerDes的設計,越來越往高頻高速發展,尤其是這一、兩年,可以看到DesignCon的文章發表,幾乎是高速SerDes相關的文章,高速的SerDes對於通道的衰減的要求越來越嚴苛,但通道也有物理瓶頸,SerDes的應用一般不會只有走在一個PCB上,就如100GBASE-KR4(802.3bj)就是應用在背板上,TX/RX分別在轉板上,利用兩個高速連接器連接在同一塊母板(Motherboard),這樣的通道損耗對於100GBASE-KR4規格的SerDes,一定必須採用Equalizer,去補償通道的損耗所造成的ISI效應。

一般通道工程師在設計高速SerDes的通道時,通常都是遵守IC設計者的規格,或者是國際標準規格,但如果你更了解Equalizer的設計,你有機會可以跟積極的與IC設計者一起設計或調整Equalizer,也許有機會幫你爭取到更寬鬆的通道規格,或者幫忙公司省下為了設計好的通道,所使用的高階PCB製成的錢。

(彷彿聽到系統廠的老闆大喊 ~OHYA~ Cost down !!)

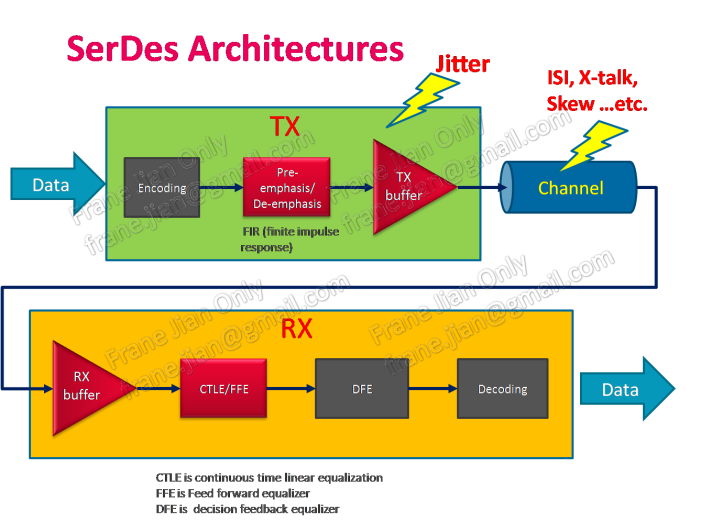

想要了解Equalizer,首先來熟悉SerDes的架構,如下圖所示,資料首先要做Coding,再經過Pre-emphasis/De-emphasis先將訊號的高低頻能量比調整後,最後再經過TX buffer將訊號提升到標準電壓準位,再送出到通道。

這時候訊號可能會遭受到一些通道所造成的問題,使訊號品質變差,常見的通道問題不外乎衰減所造成的符元干擾ISI(Intersymbol interference)問題、串音干擾、Skew等問題。

接下來因為通道所造成品質變差的訊號,先進入RX buffer載入正確負載狀況後,接下來再將訊號進入CTLE(continuous time linear equalization)或FFE(Feed-Forward Equalizer),把受損的訊號的高低頻的能量比調整後,再進入DFE(Decision Feedback Equalizer)將訊號利用多重摺積(convolution)的方法將訊號還原到較好的品質。

Why is ISI?

了解了SerDes的架構,接下來說明一下SerDes會遇到最大的問題,也就是通衰減所造成的符元干擾ISI。

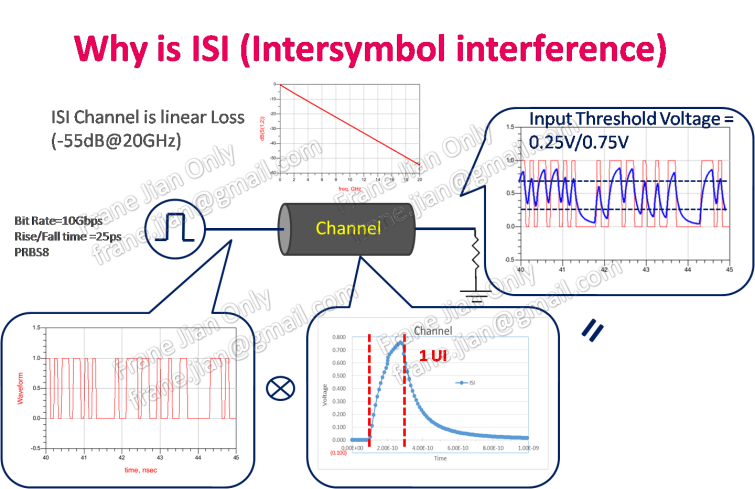

什麼是符元干擾?可以先看下面圖片,我們將-55dB@20GHz的通道,放置在訊號源及負載端的中間。

左下方的圖片是輸入訊號,右下的圖片是將通道做脈衝響應(Impulse response)變成時域的波形,也就是脈衝波(pulse wave)經過通道後的結果,再將這兩個圖片的波形去做摺積(convolution)後,就可以看到ISI的結果,也就是右上方的圖片的藍色波形。

可以看的出來,經過通道的波形,高頻成分幾乎被衰減掉,另外傳輸線無損的情況下就是類似很多幾級的電感與電容串接,所以可以看到方波經過通道後,被傳輸線的電容的影響fall time被拖的很長才結束,這就像方波經過電容下地的現象(也有一些論文說明這就像內部的多重反射所造成的多重路徑波multipath wave),方波訊號經過這樣的通道後,導致前後位元重疊導致波形變形。

如果接收端判斷數位的電壓準位分別在0.25/0.75V會有很多位元解不出來,這就是符元干擾。

De-emphasis的功用

知道了什麼是符元干擾ISI,那要如何解決這個問題呢?數位信號處理DSP的設計者,想到了利用De-emphasis在發射端就先補償通道衰減問題,接下來就來說明,De-emphasis的功用及原理。

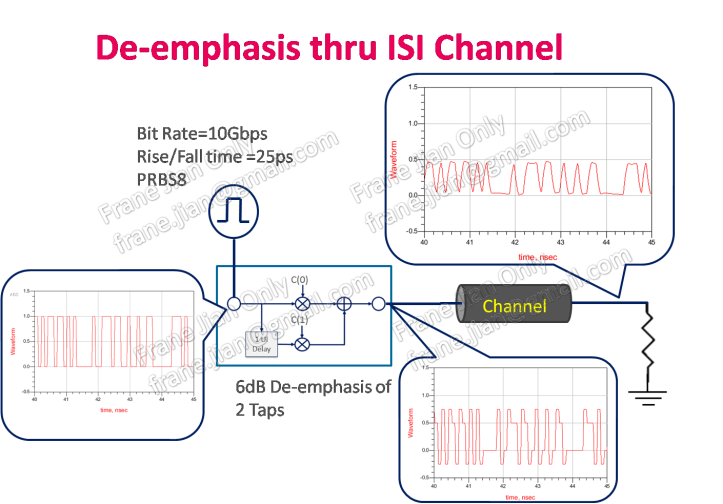

下圖為De-emphasis經過了ISI通道的波形圖,可以看到左圖為原始信號,經過了6dB De-emphasis的短位元與長位元(兩個以上的0或1)的波形都有所改變,經過了通道衰減後可以看到負載端的波形,消除了大部分的符元干擾ISI。

然而經過了6dB De-emphasis後,竟然可以消除大部分的符元干擾,那我要怎麼設定De-emphasis,接下來我們就來說明兩種常見的De-emphasis的設定方式。

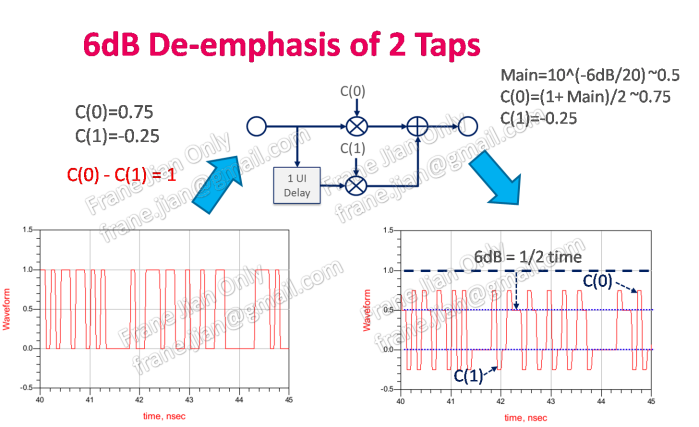

設定6dB De-emphasis of 2 Taps

這裡提供2 Taps的De-emphasis的設定值的算法,6dB De-emphasis是將全部的位元都衰減一半[10^(-6dB/20)=0.5]先將這個值定命名為Main,接下來計算C(0)的參數也就是(1+Main)/2,最後將C(0) -1就是C(1)的值,那C(0)及C(1)這兩個參數代表下圖的指標部分,也就是C(0)為最大振幅倍率,C(1)為負位元的最大振幅倍率。

Note:以上算出的值,皆為倍率值,需要乘上實際的電壓準位。

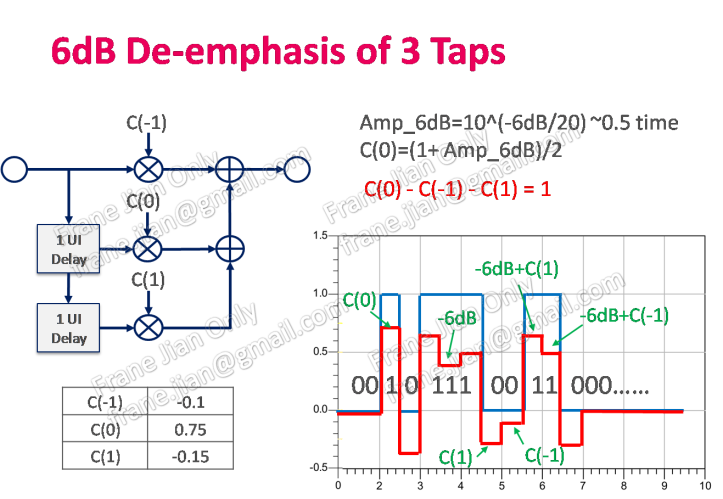

設定6dB De-emphasis of 3 Taps

那如果是3 Taps的6dB De-emphasis,我們要怎麼設定裡面的參數呢?

其實算法與2 Taps很像,一樣將全部的位元都衰減一半[10^(-6dB/20)=0.5]先將這個值定命名為Amp_6dB,接下來計算C(0)的參數也就是(1+Amp_6dB)/2,接下來就是設定C(1) & C(-1),只要符合C(0) – C(-1) – C(1) = 1的原則即可,一般會將C(1)設定的比C(-1)還要大,如下圖所示。

那C(0) C(-1) C(1)分別代表波形的哪些地方呢?我們可以參考下圖的標示,大家在自行理解。

De-emphasis, How to work?

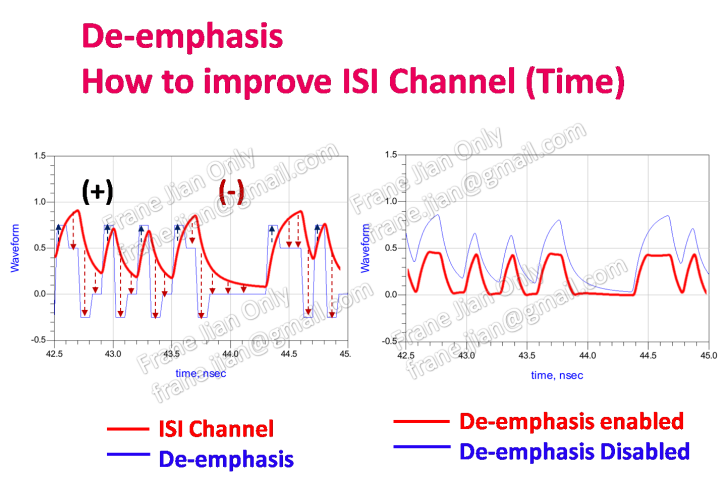

瞭解了De-emphasis如何設定後,接下來說明De-emphasis是如何消除符元干擾ISI,從時間領域(Time domain)來說明,請看下面的圖左,將訊號經過ISI通道的波形,與2階的6dB De-emphasis的波形疊在一起,可以看到ISI通道的高頻衰減的部分被De-emphasis的預先提升的波形拉起,其ISI通道的fall time被拖的很長才結束的波形,也被De-emphasis經過一個位元(UI)就下降的波形,給往下拉。

就這樣De-emphasis與ISI通道效應的一消一長的處理,可以得到消除大部分ISI的效應,如下面右圖所示。

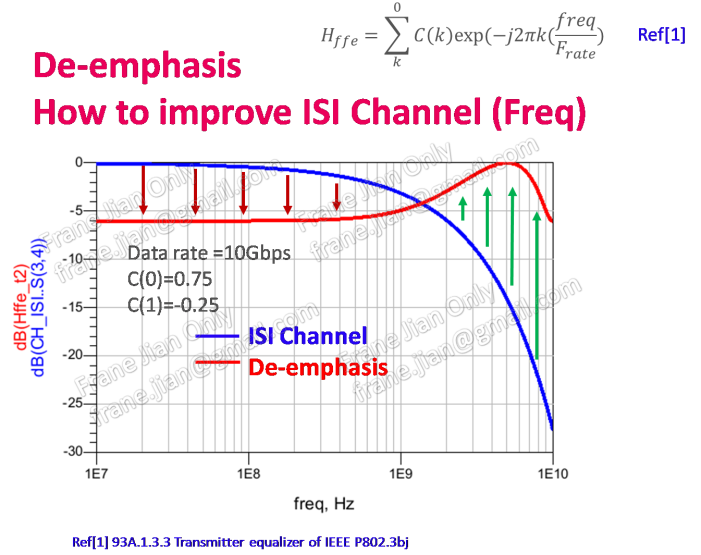

那如果去看頻率響應,其De-emphasis是如何消除ISI效應。

可以利用IEEE P802.3bj的Transmitter equalizer公式,畫出De-emphasis頻率響應,如下圖的紅色曲線,然後再將ISI通道(藍色曲線)的頻率響應疊在一起,這樣就可以知道De-emphasis頻率響應,就是將低頻往下衰減,再將高頻成分往上拉,這樣可以將整體的頻率響應盡量拉平,以消除ISI通道效應。

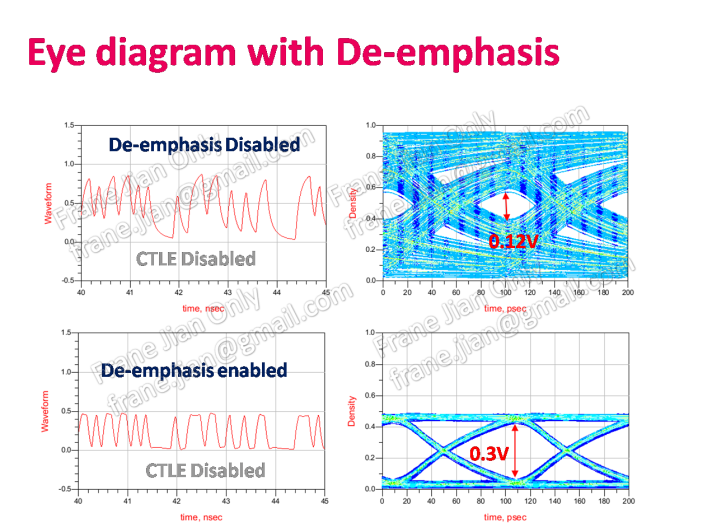

瞭解了De-emphasis是如何消除ISI效應後,接下來比較有無De-emphasis的眼圖的結果,可以看到下圖,沒有De-emphasis的眼圖其眼高只有0.12V,其有開De-emphasis的眼圖的眼高可以達0.3V,等於眼高比沒有De-emphasis的高度多了快3倍高。

不過有De-emphasis的波形會犧牲它的振幅,這也算是De-emphasis的缺點吧,但這個部分可以在TX或RX的部分增加一個放大器,也可以解決De-emphasis振幅變小的缺點,但這也增加了IC的大小,以及IC的功耗。

CTLE的功用

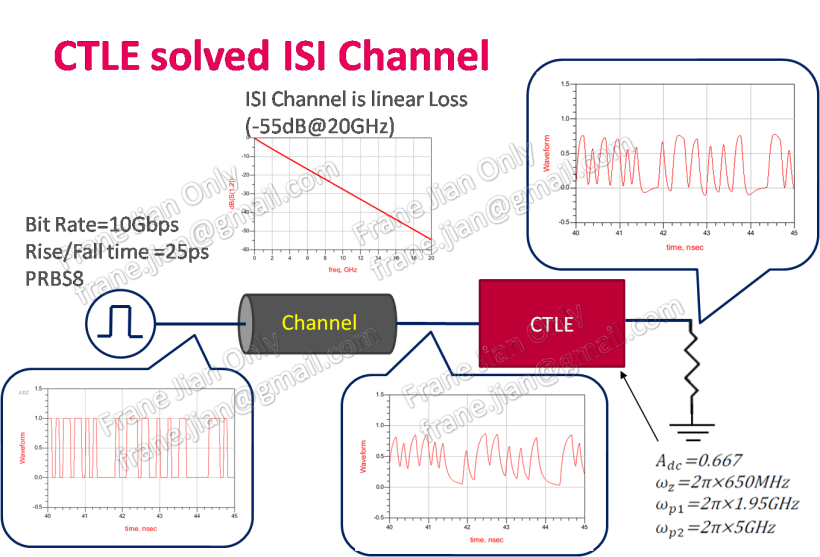

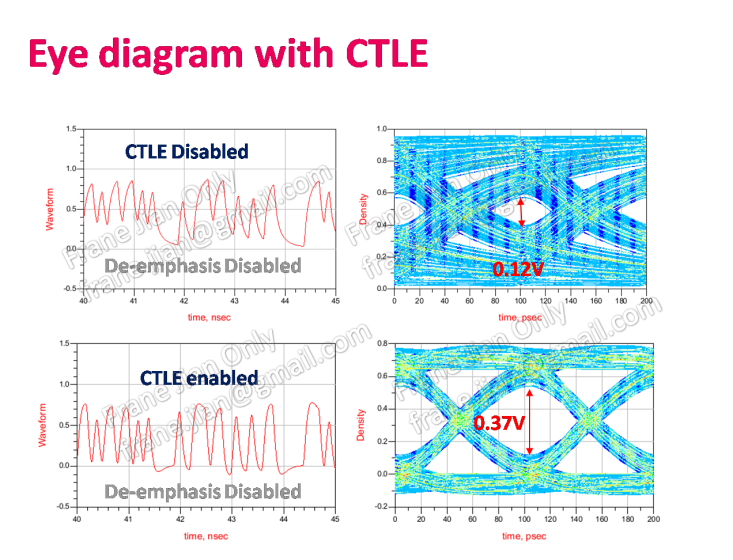

RX的部分要如何解決ISI的問題,這邊做一個實驗,將訊號經過通道後產生ISI的效應,接下來將ISI效應的訊號經過CTLE的功能後,可以看到ISI的效應幾乎被抑制掉了,如下圖所示。

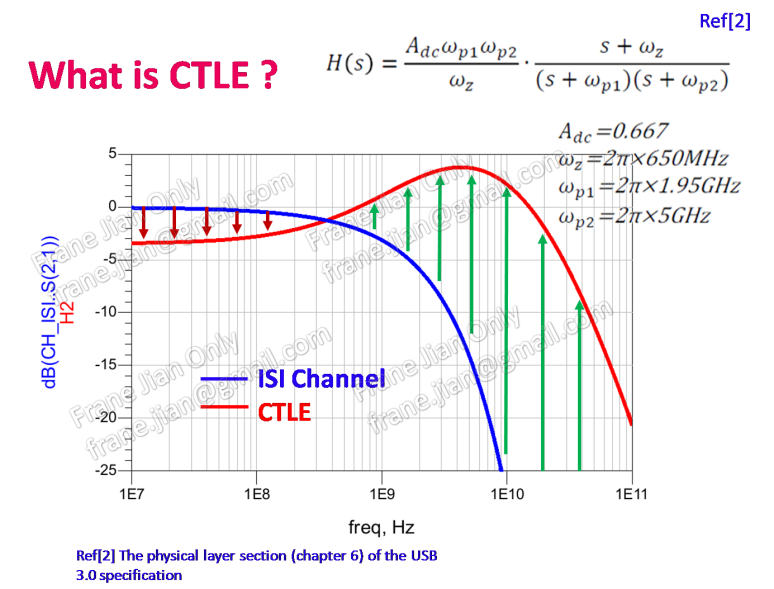

那CTLE是如何抑制ISI的效應,可以看到下圖,CTLE的頻率響應的曲線(紅色),與通道的頻率響應的曲線(藍色),將兩曲線疊在一起,可以了解CTLE就像De-emphasis的原理差不多,就是將通道的低頻成分降低,並將通道的高頻成分拉高,將通道的頻率響應盡量修正成水平。

其CTLE的調整參數為Adc,Wz,Wp1,Wp2,讀者可以利用調整這幾個參數,帶入下圖的方程式,就可以依照通道的頻率響應,調整適合的參數值。

下圖為比較有無開CTLE的功能的眼圖比較,可以看到都沒有開化器的眼圖,眼高約0.12V,開了CTLE的功能的眼圖,眼高約0.37V,其有開CTLE的功能的眼圖比沒有開的整整眼高,高了3.5倍左右。

Best Equalizer?? Best Channel??

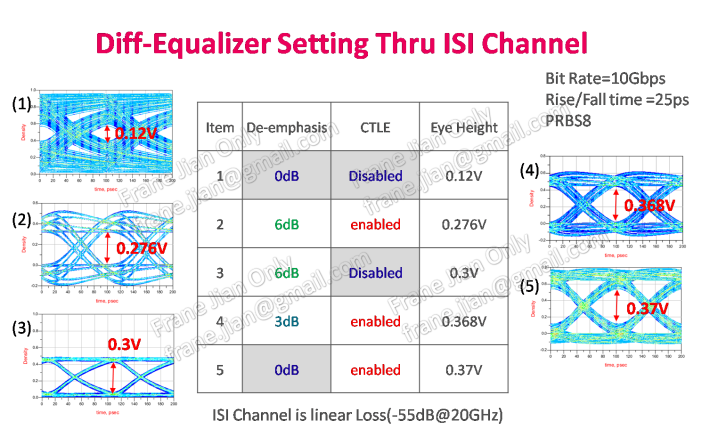

那什麼是最好的等化器,什麼為最好的通道設計,下面圖利用線性衰減的通道,做了一系列的等化器實驗。

(1)首先Item-1是都沒有開等化器的情況下,眼高是最低的

(2)接下來先看Item-3在開了6dB De-emphasis,且沒有開CTLE眼高約0.3V。

(3)然後我們會想如果開了6dB De-emphasis,而且也開啟CTLE,預期眼高會更高吧。但實驗結果如Item-2,眼高沒有比Item-3高,直接去看Item-2的眼圖,可以直接了解,等化器將通道過補償了,所以導致眼高沒有比較高。

(4)有了前面的例子,這個案例就將De-emphasis降為3dB,並且開啟CTLE功能,實驗結果眼高可以達到0.368V。

(5)最後實驗將De-emphasis關閉,並且開啟CTLE功能,實驗結果得到為所有實驗組,眼高最高的結果。

這樣的結果,直覺會想到,不需要De-emphasis,而只要有CTLE功能就可以達到抑制ISI的問題。

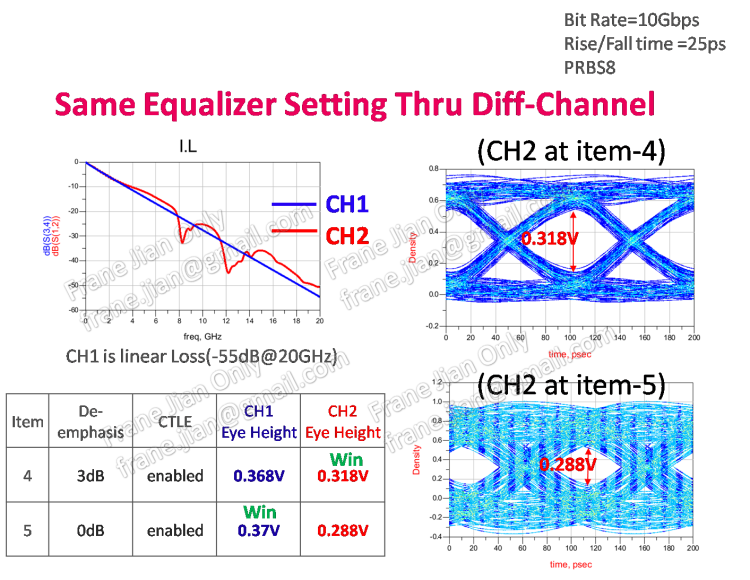

其實不然,下一個實驗,使用兩種不同的通道,其衰減量大致相同,不過CH2的通道,多了一些通道阻抗不匹配所召成的反射量,導致部分頻率有較大的衰減,這一般SerDer不想遇見的通道問題。

這個實驗等化器的設定不變,我們比較Item-4 & 5這兩個實驗組,如下圖所示。

實驗結果如下

(1)相同的等化器設定,在線性衰減的通道CH1,Item-5的眼高比Item-4的眼高還要高。

(2)但一樣的等化器設定,有部分衰減量較大的通道CH2,實驗結果與前一個相反,其Item-4的眼高比Item-5的眼高還要高。

Summary

1.通道的設計者,其實可以更積極的參予整個SerDes的設計,比如等化器的優化。

因為現今的SerDes往越來越高速發展,未來的通道設計只會會越來越嚴苛,然而通道往往會有物理限制,如果通道的設計者有調整等化器的能力,就可以推薦SerDes設計者,優化後的等化器參數值,或提供較好的等化器架構,增加自己的技術價值。

2.通道的設計者也可以知道,為什麼會有這些通道規格,並了解SerDes的極限在哪裡,而不會一昧的被動採用所有通道的規格。也許可以不需要這麼嚴苛的通道需求,進而去採用較低的製程規格去做通道,達到降低成本的目的。

3.世界上沒有最佳的等化器,只有在不同環境下,最平衡的等化器設定。等化器設定必須符而不同的通道環境去設定。

參考文獻

Ref[1] 93A.1.3.3 Transmitter equalizer of IEEE P802.3bj

Ref[2] The physical layer section (chapter 6) of the USB 3.0 specification

[重大更新]

由於之前文章將De-emphasis誤寫成Pre-emphasis,在此特別說明,文章內容以更新完成。

感謝(群暉科技) Alex Chiu 的來信提醒,下面為Alex 提供的資訊。

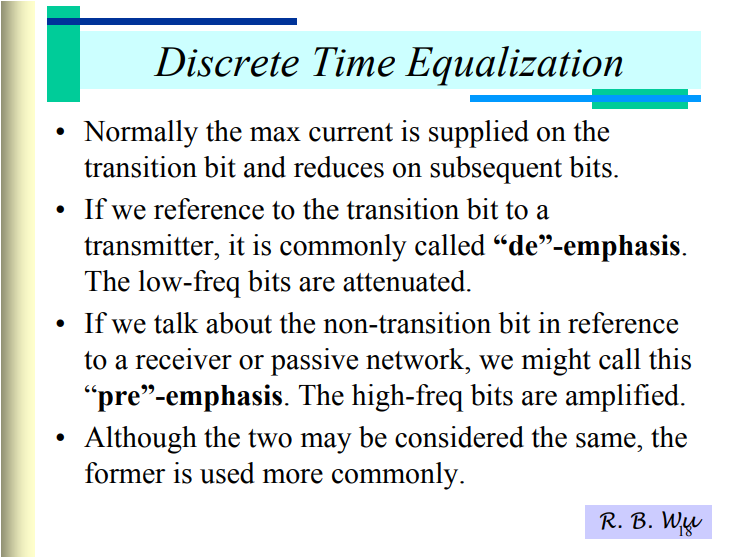

Pre-emphasis與De-emphasis的差別,一個是加電壓給高頻(主動),另一個是衰減低頻(被動)。

Alex的參考資料如下,提供給大家參考

(1)

在Altera這篇的第九頁第二段當中提到

Altera’s transmitter implements both pre-emphasis and de-emphasis. It increases the high-frequency components and decreases the low-frequency components. The total amount of emphasis is the difference between pre-emphasis and de-emphasis. The advantage of this implementation is that it dissipates less power than the traditional pre-emphasis and achieves the same amount of emphasis.

(2)

Click to access SI10_Equalization.pdf

台大吳瑞北老師SI講義中第16頁

(3)

影片的第4:48秒

(4)

第八頁有說明De-emphasis